# 2025 International Solid-State Circuits Conference (ISSCC) Review

한양대학교 ERICA 전자공학부 김종석 교수

**Topic: Sensor**

## Session 6: Imagers and Displays

ISSCC 2025의 Session 6는 Imagers and Displays 라는 주제로 총 10편의 논문이 발표되었다. 이 세션에서는 LiDAR 센서, CMOS 이미지 센서, OLED 디스플레이 드라이버, 터치스크린 컨트롤러에 이르는 다양한 센서 회로 및 디스플레이 회로 연구들이 다수 발표되었다.

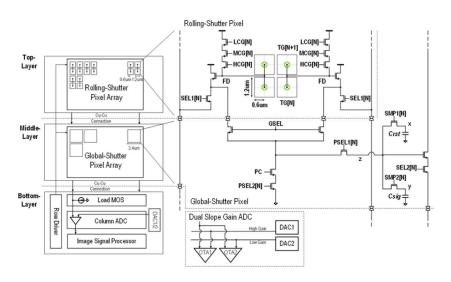

#6-1 삼성전자, 모바일 애플리케이션을 위한 전환 가능한 3층 적층 hybrid shutter (HS) CMOS image sensor (CIS)를 제안하였다. 이 센서는 1.2μm-pitch 50Mpixel rolling shutter (RS)와 2.4μm-pitch 12.5Mpixel global shutter (GS) 모드 간 전환이 가능하다. RS 모드는 30FPS로, GS 모드는 95FPS로 작동한다. Shutter회로는 65nm CIS 공정, logic은 28nm CMOS 공정을 통해 제작되었으며, 3층 적층 구조로 상층은 RS용, 중간층은 GS용, 하층은 logic 회로용으로 설계되었다. 기존 RS CIS 의 성능과 기능을 유지하기 위해 상층에는 conventional 4-transistor pixel 구조를 적용했으며, GS 모드에서의 random noise (RN) 성능 향상을 위해 중간층에 고용량 DRAM capacitor 기술을 적용하였다. 이를 통해 low conversion gain (LCG)에서 52ke-의 full well capacity (FWC), high conversion gain (HCG)에서 2.4e-의 낮은 RN을 달성했다. 또한 high dynamic range (HDR)를 위해 dual slope qain (DSG) 모드를 적용하여 HDR 성능을 6dB 향상시켰다.

[그림] #6.1 논문에서 제안하는 3층 적층 HS 구조.

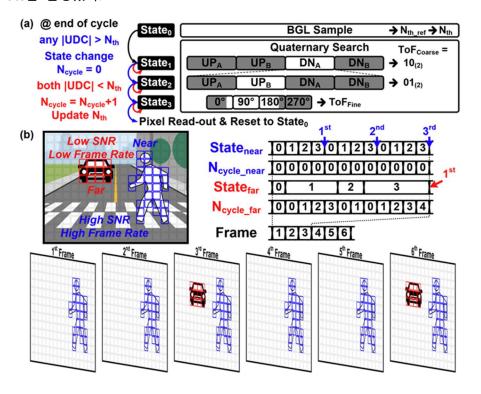

#6-2 UNIST, 외부 구성요소 의존 없이 pixel 자체적으로 threshold ( $N_{th}$ )을 제어하는 background light (BGL) 적응형 Nth 기반 asynchronous  $160 \times 90$  pixel array 플래시 LiDAR 센서를 제안하였다. 기존 LiDAR 센서가 최악의 SNR 조건을 갖는 pixel에 의해 프레임 속도가 제한되는 것과 달리, 제 안하는 LiDAR 센서는 각 pixel이 BGL 강도로부터  $N_{th}$ 를 설정해 time-of-flight (ToF) 값을 검증하고 integration time을 동적 조절한다. Bitwise arithmetic unit으로 pixel 내  $N_{th}$  계산이 가능하며, 검증된 pixel만 순차적으로 읽어낸다. 90nm BSI 공정으로 제작되었으며, 센서는 1.5-to-22.5m 범위에서 6cm precision, 8cm accuracy를 달성했고, 30klux 조명에서도 21m 거리에서 95% 이상 true detection rate를 달성했다.

[그림] #6.2 논문에서 제시된 asynchronous pixel의 개념적 작동 원리.

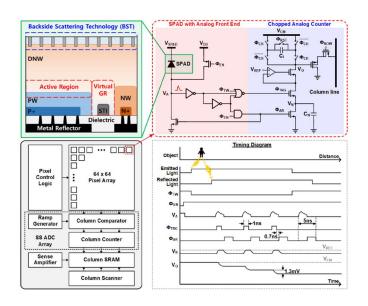

#6-3 연세대학교, 76m 거리와 120klx background light (BGL)에서 작동하는 single-photon avalanche diode (SPAD) 기반 flash LiDAR 센서를 제안했다. 핵심 기술은 BGL을 억제하면서 노출시간을 유지하는 multiple-chopping analog counter 이다. 기존 analog counter 의 선형성 제한 및 BGL 에 의한 saturation 문제를 해결하기 위해 chopped charge-injection 방식을 제안했다. 이 방식은 one discharge path를 사용하여 균일한 counting step을 제공하고 gain mismatch 문제를제거했다. 제안하는 회로는 110nm BSI CIS 공정으로 제작되었으며, multiple-chopping 기술을 통해 counter saturation issue를 해결하여 120klx 의 BGL 의 조건하에 최대 76m 거리에서 6.4cm 의 depth precision, 33%의 fill factor를 달성했다.

[그림] #6.3 논문에서 제안하는 SPAD-based iToF sensor의 구조 및 동작.

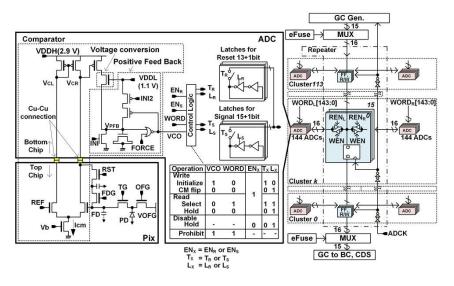

#6-5 SONY, Pixel-parallel ADC를 활용한 25.2Mpixels, 120 FPS full-frame global shutter (GS) CMOS 이미지 센서를 제안했다. Rolling shutter (RS) 센서의 움직이는 물체 왜곡, flicker effect, flash band 문제를 해결하기 위해 global shutter (GS) 기술을 적용했다. Pixel-parallel ADC의 parallelism을 활용하여 ADC comparator 소비전류를 25nA로 감소시켰고, ADC의 comparator에 NMOS capacitor를 추가하여 random noise를 줄였다. Back-illuminated pixel chip은 90nm, logic chip은 40nm 공정을 이용해 제작하였으며, back-illuminated pixel chip과 logic chip을 3µm pitch의 Cu-Cu hybrid bonding으로 연결시켰다. 사용된 ADC는 5.94µm pitch의 single-slope pixel-parallel ADC로 0dB gain에서 2.66 e-rms의 random noise와 14bit resolution을 달성하였다. 따라서 본 논문에서 제안한 CMOS 이미지 센서는 14bit resolution으로 25.2Mpixels을 120FPS에서 판독할 수 있으며, 75.5dB의 dynamic range와 1545mW의 소비전력, 0.083e-rms·pJ/step의 FoM을 달성했다.

[그림] #6.5 논문에서 제안하는 이미지 센서 readout 회로의 구조.

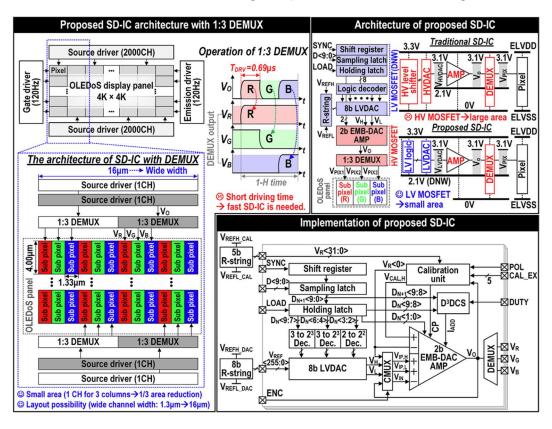

#6-7 한양대학교, AR/VR 기기용 OLED-on-Silicon (OLEDoS) display를 위한 10bit source driver IC 로, 저면적, 고균일, 고속구동의 특성을 갖는다. All-channel automatic offset calibration (ACAOC)를 통해 모든 AMP의 offset 전압을 동시에 보상하여 채널간 균일도를 향상시켰으며, data-difference-dependent dynamic current source (D³DCS)을 통해 대기전류 증가 없이 slew-rate를 향상시켜 구동속도를 향상시켰다. 또한 1:3 demultiplexer (DEMUX) 구조 및 low-voltage (LV) DAC기술을 적용하여 회로 면적을 감소시켰다. 제안하는 회로는 65nm CMOS 공정으로 제작되었으며, channel당 2,273µm²의 면적, 1.9mV의 deviation of voltage outputs (DVO), 0.69µs의 settling time을 달성했다.

[그림] #6.7 논문에서 제안하는 SD-IC의 구조.

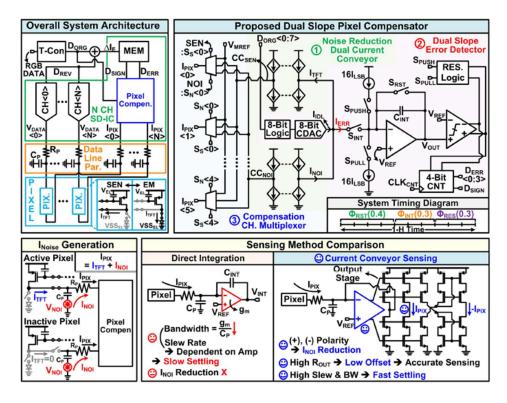

#6-8 고려대학교, AMOLED 디스플레이용 external compensation circuit으로, 패널 pixel 회로의 error를 실시간으로 보상하는 특징을 갖는다. Noise-reduction dual current conveyor (NDCC)를 사용하여 display panel noise로부터 간섭을 받지 않으면서, OLED pixel에 사용된 low-temperature polycrystalline silicon (LTPS) thin-film transistor (TFT)의 non-uniformity를 감지한다. 특히 mismatch 에 민감한 integrator를 필요로 하지 않는 dual slope error detector (DSED)를 통해 pixel error를 감지한다. 또한 compensation channel multiplexer (CCM)를 통해 하나의 compensator가 여러 source driver channel을 지원할 수 있게 하여 회로 면적과 전력소비를 크게 줄였다. 250nm 2.5V/5V 공정으로 제작되었으며, channel당 4442.8μm²의 면적과 13.3μW의 전력소비를 달성했으며, 300kHz에서 최대 630nApp의 panel noise tolerance를 달성했다.

[그림] #6.8 논문에서 제안하는 pixel compensator 의 구조 및 동작.

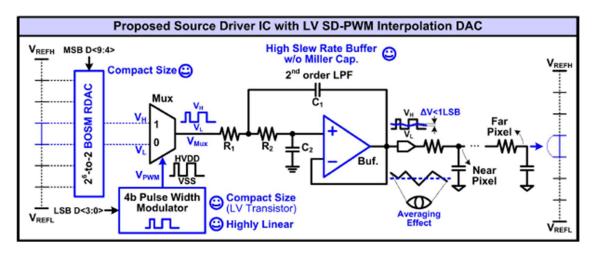

#6-9 고려대학교, 디스플레이용 10bit source driver IC로, delta-sigma pulse width modulation (SD-PWM)을 활용한 low-voltage digital interpolation을 통해 면적을 크게 감소시킨 특징을 갖는다. 4bit low-voltage pulse width modulator와 second-order RC low-pass filter 구성의 SD-PWM interpolation DAC와 MSB switching binary-tree overlap switch merging (BOSM) 기술로 6bit resistor-string DAC의 transistor 수를 80.7% 감소시켰다. 65nm CMOS 공정으로 제작되었으며, 최대 DNL 0.42LSB, 최대 INL 1.44LSB, static current 1.5µA, channel 당 1884µm²의 면적을 달성했다.

[그림] #6.9 논문에서 제안하는 10bit SD-IC의 구조 및 동작원리.

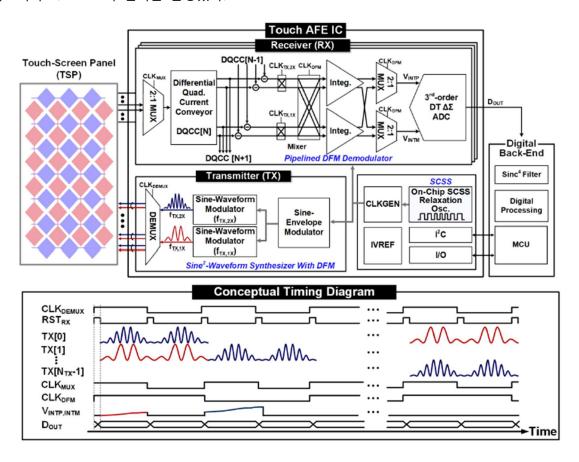

#6-10 성균관대학교, 자동차용 터치스크린 센서를 위한 electromagnetic interference (EMI) 감소 기술을 적용한 touch analog front-end (AFE) integrated circuit을 제안했다. 자동차용 터치스크린 센서는 EMI를 방출하여 차량 내 다른 전자 부품에 영향을 줄 수 있는데, 이 문제를 해결하기 위해 sine² waveform shaping 기술, sine-chirp spread spectrum (SCSS) clocking, 그리고 pipelined dual-frequency modulation (DFM) 방식을 도입했다. 80nm CMOS 공정으로 제작되었으며, CISPR 25 Class 5 규격을 준수하면서도 높은 SNR(최대 49.6dB)과 frame rate(200Hz)를 달성했으며, 10.5mW의 전력소비와 2.21mm²의 면적을 달성했다.

[그림] #6.10 논문에서 제안하는 터치 AFE IC의 구조와 timing diagram.

#### Session 27: Sensor Interfaces

ISSCC 2025의 Session 27은 sensor interfaces 라는 주제로 총 5편의 논문이 발표되었다. 이 세션에서는 자이로센서, 홀 센서, CT 센서, 그리고 두 편의 온도 센서의 판독 회로에 관한 연구들이 발표되었다.

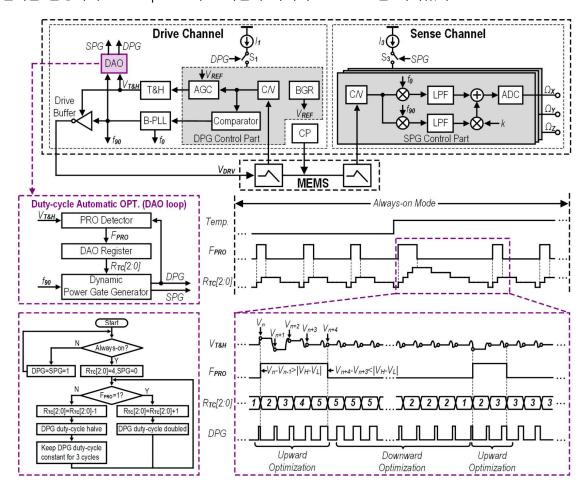

#27-1 Xidian University, Wearable 기기 및 mobile 장치에서 always-on mode로 동작하는 MEMS gyroscope sensor readout에 대한 논문이다. Always-on mode로 동작하는 MEMS gyroscope sensor 는 적용되는 application 특성에 따라 빠른 wake-up time과 저전력 특성을 필요로 한다. 기존 연구에서는 burst-mode PLL (BPLL) 기법을 사용하여 저전력과 빠른 wake-up time을 구현했지만, 온도 변화로 발생하는 parasitic relaxation oscillation (PRO) 현상으로 인해 안정성 문제가 발생한다. 본 논문에서는 duty-cycle automatic optimization (DAO) 기법을 적용한 chip을 180nm BCD 공정으로 제작했으며, PRO 현상에 의한 불안정성을 ±5% 내로 유지하여 안정적인 성능을 달성했다. 또한 three axis system에서 always-on mode의 wake-up time은 2.8ms와 동시에 847nA 수준의 소비전력을 달성하여 wake-up time과 소비전력 사이의 trade-off 를 극복했다.

[그림] #27.1 논문에서 제안하는 duty-cycle automatic optimization (DAO)가 적용된 BPLL-based always-on MEMS gyroscope 시스템의 구조 및 동작.

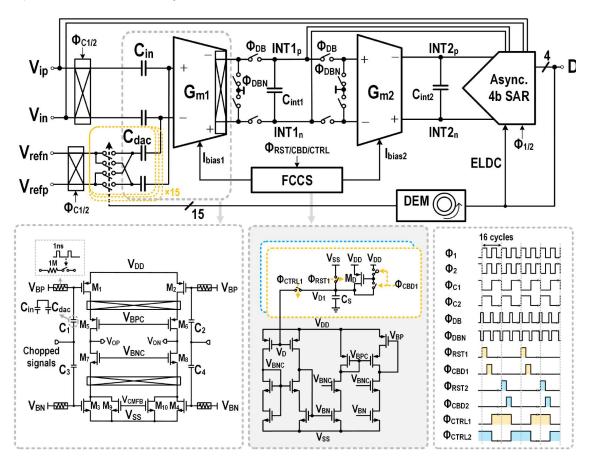

#27-3 Zhejiang University, 본 논문은 IoT application과 low power sensor 시스템을 위한 BW/power의 확장성을 갖는 low noise sensor 인터페이스 회로를 제안했다. 제안하는 회로는 Gm-C ΔΣ modulator (Gm-C CTDSM)와 frequency-controlled current source (FCCS)을 이용하여 연속시간 신호를 처리하며, 기존의 discrete-time ADC 방식과 비교하여 더 낮은 input-referred noise density를 갖는다. 130nm CMOS 공정으로 제작되었으며, 225배의 BW/power 확장성, 46nV/rtHz의 input referred noise density, 85dB의 SNDR을 달성했다.

[그림] #27.3 논문에서 제안하는 current-reuse pseudo-differential amplifier, FCCS operating in a ping-pong mode가 적용된 CT sensor의 전체 system.

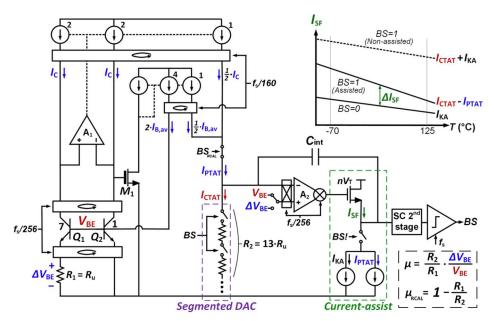

#27-4 TU Delft, Noise-optimized charge-balancing scheme과 current-assisted amplifier를 적용한 BJT-based temperature sensor를 제안했다. 제안하는 temperature sensor는 높은 SNR을 달성하기 위해 noise-optimized charge balancing scheme을 활용했다. 또한 높은 정확도를 위해 segmented DAC를 적용하여 기생 capacitance에 의한 영향을 줄였으며, resistor calibration 기법, chopping 기법과 dynamic element matching (DEM)을 적용하여 mismatch 및 noise로 인한 error를 감소시켰다. 또한, 높은 energy efficiency를 위해 필요한 순간에만 추가적인 current를 제공하는 current-assist technique을 사용했다. 제안하는 회로는  $0.18\mu m$  CMOS 공정으로 제작했으며,  $f_s=50kHz$ 에서 0.79mK,  $f_s=400kHz$ 에서 2.3mK의 해상도를 제공한다. 또한,  $80fJ\cdot K^2$ 의 FoM과  $0.05mm^2$ 의 면적을 달성했다.

[그림] #27-4 논문에서 제안하는 noise-optimized charge-balancing scheme의 구조.

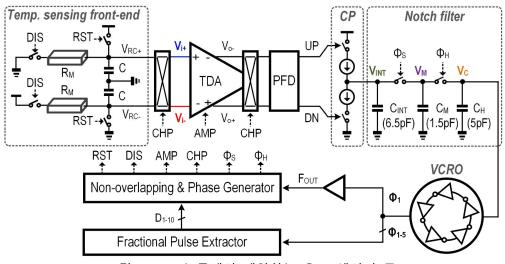

#27-5 University of Macau, Wire-metal 기반 저면적 온도 센서에 대한 논문이다. 제안하는 온도 센서는 fractional-discharge 방식의 frequency-locked-loop (FLL)과 time-domain amplifier (TDA)를 활용하여 온도를 측정한다. Fractional-discharge 기법을 통해 capacitor 방전 시간을 단축하여 큰 면적의 저항을 사용하지 않더라도 정확한 온도 측정이 가능하며, TDA의 chopping 기법을 적용해 DC offset과 1/f noise를 제거했다. 28nm 공정으로 제작했으며, 센서는 -40-125℃ 범위에서 ±0.2℃ (3♂) 이내의 높은 정확도를 유지하며, 45fj·k²의 FoM을 달성하였다. 또한, 28/65nm의 공정 기반 저항형 온도센서 대비, 전력 소모 12배 감소, 면적 2.2배 감소 등의 개선을 이루어 system-on-chip 환경에서의 활용 가능성을 높였다.

[그림] #27-5 논문에서 제안하는 온도 센서의 구조.

### **Session 28: Capacitive Sensor Readout**

ISSCC 2025의 Session 28은 capacitive sensor readout 라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는  $\Delta\Sigma$  modulation, SAR에 이르는 센서 판독 회로에 관한 연구들이 다수 발표되었다.

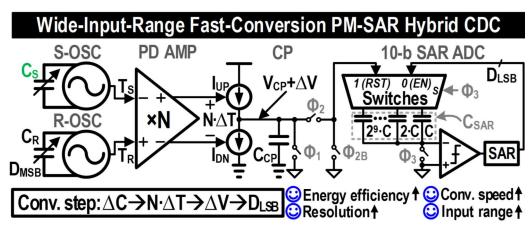

#28-1 KAIST, 넓은 입력 범위와 빠른 변환 속도를 동시에 구현한 PM-SAR hybrid capacitance-to-digital converter (CDC)를 제안한다. 제안하는 CDC는 period-modulation (PM) 방식과 successive approximation register (SAR) 방식을 결합한 하이브리드 구조를 채택하며, 센서 및 기준 캐패시턴스  $(C_S,C_R)$ 는 발진기 (S-OSC, R-OSC)에 의해 주기 정보  $(T_S,T_R)$ 로 변환되고, 이 주기의 차이  $(\Delta T)$ 를 period-difference amplifier (PD AMP)가 증폭한 후, charge pump (CP)를 통해  $\Delta T$ 가  $\Delta V$ 로 변환되며, 최종적으로 SAR ADC에서 디지털 값  $(D_{LSB})$ 로 변환된다. 그 결과, 제안하는 CDC는 65nm 공정에서 제작하였으며, 18.5nF의 입력 범위와 6.1 $\mu$ s의 변환 속도 (@18.1 $\mu$ s)를 달성하며, 기존 CDC가 갖는 해상도와 변환 속도 간의 trade-off를 극복하였다. 또한, 138fJ/conv.-step의 FoM $_W$ 와 173.9dB의 FoM $_S$ 를 달성했다.

[그림] #28-1 논문에서 제안하는 PM-SAR hybrid CDC의 구조.

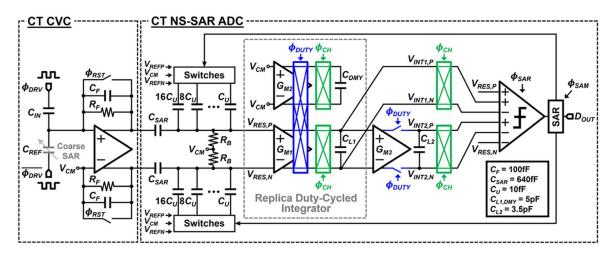

#28-2 KAIST, continuous-time (CT) 도메인에서 highpass (HP) noise-shaping scheme을 적용한 continuous-time noise-shaping SAR capacitance-to-digital converter (CT NS-SAR CDC)를 제안한다. 제안하는 CDC는 continuous-time capacitance-to-voltage converter (CT CVC)를 통해 입력 신호를 전압으로 변환한 후, HP noise-shaping을 적용한 SAR ADC를 이용하여 양자화 한다. 또한, chopper-based CP HP loop filter를 통해 flicker noise를 제거하고 anti-aliasing 기능을 제공하며, replica duty-cycled integrator (RDI)를 적용해 전력 소모를 줄이고, error-charge integration을 방지하여 안정적인 동작을 유지한다. 제안하는 CDC는 0.18μm CMOS 공정으로 제작되었으며, 총 전력 소모 15.2μW (@1.2V supply)에서 189.3dB의 FoM<sub>S</sub>, 14.5fJ/conv.-step의 전력 효율, 17.7aF<sub>rms</sub>의 해상도를 달성했다.

[그림] #28-2 논문에서 제안하는 CT CVC와 CT NS-SAR ADC의 구조.

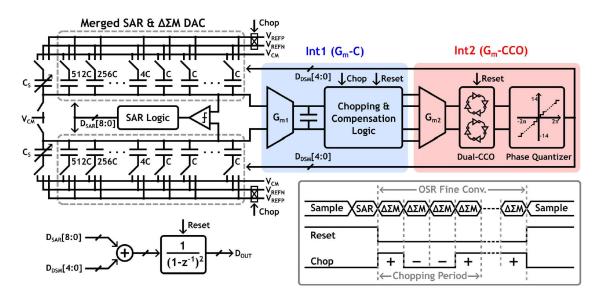

#28-3 Peking University, Chopping 기반 kT/C 노이즈 제거 기법과 add-then-subtract phase-domain lead-compensation technique을 적용하여 고해상도와 높은 에너지 효율을 달성한 capacitance-to-digital Converter (CDC)를 제안하였다. 또한,  $2^{nd}$ -order incremental-zoom 아키텍쳐를 적용하여 저전력으로  $8.7aF_{rms}$ 의 캐패시턴스 측정을 가능하게 한다. 제안하는 CDC는 28nm CMOS 공정에서 제작되었으며,  $70.1\mu$ W의 전력을 소비하면서 93.8dB의 SNR을 달성하였다. 기존 방식보다 더 낮은 샘플링 노이즈를 가지며,  $10.4\mu$ S의 측정 시간 내에서도 높은 정확도를 유지하다. 특히,  $FoM_S$ 이 185.2dB로  $100\mu$ S 이하의 측정 시간을 가지는 기존 CDC 중에서 최고 성능을 달성하였다.

[그림] #28-3 논문에서 제안하는 incremental-zoom CDC의 구조 및 timing diagram.

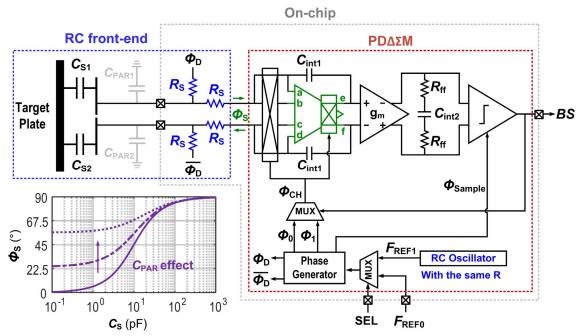

#28-4 Tsinghua University Differential RC front-end와 phase-domain-delta-sigma modulator (PDΔΣM)을 적용하여 높은 정확도를 갖는 capacitive displacement sensor를 제안한다. 센서는 floating target 환경에서도 안정적으로 동작할 수 있도록 differential RC front-end를 통해 sensing capacitance를 phase shift로 변환한 후, 이를 PDΔΣM을 이용해 bitstream으로 변환하여 displacement 정보를 digital output으로 출력하는 구조를 갖는다. 또한, feedforward-compensated two-stage opamp를 적용함으로써 input impedance를 최소화하여 phase-sensing error를 줄였으며, 기준 주파수 (F<sub>REF</sub>)의 온도 변화 영향을 최소화하기 위해 temperature coefficient (TC)가 매칭된 resistor와 capacitor를 사용하여 TC accuracy를 개선하였으며, chopping과 notch-filtering을 통해 DC offset과 low-frequency noise를 제거하고 output frequency jitter를 감소시켜 센서의 안정성을 높였다. 제안하는 CDC는 0.18μm 공정으로 제작되었으며, 143dB 이상의 dynamic range, 21.3aF<sub>rms</sub>의 resolution, 119dB의 CMRR (@DC)을 달성하였다.

[그림] #28-4 논문에서 제안하는 RC front-end와 PD $\Delta$ ΣM의 구조.

# 저자정보

#### 김종석 교수

● 소 속 : 한양대학교 ERICA 전자공학부

• 연구분야 : Display circuit, sensor circuit, biomedical circuit

• 이 메 일 : jskim383@hanyang.ac.kr

● 홈페이지: https://www.SIDLAB.net